The IC 4046 is a Phase-locked loop IC of CMOS digital (combined analog and digital chip).

A Phase-locked loop(PLL) has a voltage-controlled oscillator(VCO).

The VCO signal and an input signal are sent to a phase comparator which generates an error voltage part to any difference in frequency between two signals.

The error voltage adjusts the VCO frequency to match that of the input signal.

Thus the PLL can track an input signal.

Or only the VCO function can be used.

The specifications and CMOS IC use and handling caution.

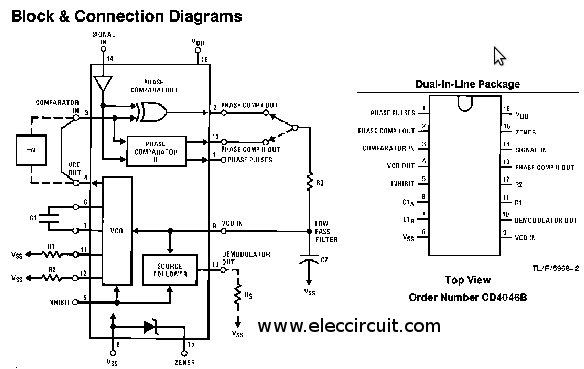

In Figure 1 is a block diagram connections of IC 4046

Feature of CD4046

The supply voltage Range: +3 volts to +18 volts VCO frequency linearity: 1% typical.

It is a CMOS chip that requires special practice.

There’s much more about CMOS in your digital logic workbook.

The follow these guidelines for use.

1. Connect unused inputs (pins 3,5,9 and 14) to ground or the positive supply voltage.

2. Pins 6,7,10,11,12 and 15 should be lift disconnected if unused.

3. The voltage at a CMOS gate input much not exceed the supply voltage.

4. Never insert or remove a CMOS chip into or from the PCB or socket IC of your projects or learning lab unless the power switch is OFF.

How to use CD4046

Let’s see the circuits using CD4046. We get more ideas better.

Phase-locked oscillator circuit,100Hz-10KHz square wave

This is a Phase-locked oscillator circuit,100Hz-10KHz square wave, the other circuit one interesting.

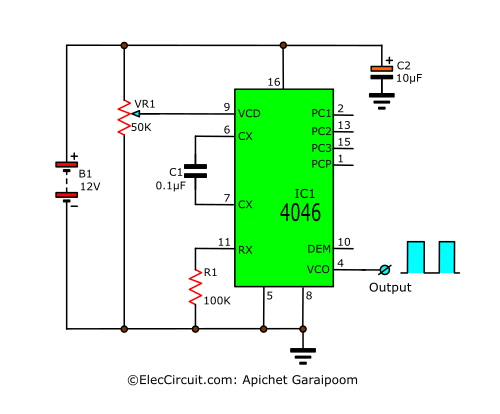

The CMOS IC is selected for this case. It will be Phase Lock Loop IC is CD4046. It hs characteristics the setting circuit as Figure 1.

Using the voltage control frequency. The voltage that is derived from pin 9 of IC1 voltage adjustment of VR1. Including C1 is connected between pin 6 and pin 7 of IC1.

Minimum and a maximum frequency of this circuit are determined by R1 and R2, respectively.

How it works

We can generate frequencies from 1 Hz to 1 MHz.

But it must depend on the devices connected to the outside that much.

This creates a cycle frequency from 100 Hz to 10 kHz.

Figure 1 The 100 Hz to 10 kHz square wave generator by Phase Lock Loop IC

For some people, it may seem too little. Would increase the frequency to the next, but do not want to waste more money.

You can add up to the other frequency of about 10 kHz. Just remove R2 from the circuit itself.

Which this R2 determines the frequency in use. By the R2 value of this, would be to refer to R1, it must be 10 times greater than R1.

For R1 and C1 will determine the minimum frequency or low voltage pin 9 of IC1. And at this pin 9 if there is low voltage, the frequency output or at pin 4 of IC1 will be low too.

On the other hand, the pin 9 has high voltage, the output frequency will be higher as well. Understanding is simple enough voltage is proportional to the frequency.

C1 of the circuit, we can change, For the frequency range, we need. See Table 1. So I like to use bands to choose it.

C1 determines the frequency of use.

C1 (25V) Frequency range

1uF 0-100Hz

0.1uF 10Hz – 1kHz

0.01uF 100Hz – 10kHz

How it builds

This project is a few components so can assemble on the universal PCB board. But can make a PCB. You should be careful about the polarity of the electrolytic capacitors and IC1 correctly.

Universal tester circuit with VCO(voltage controlled oscillator)

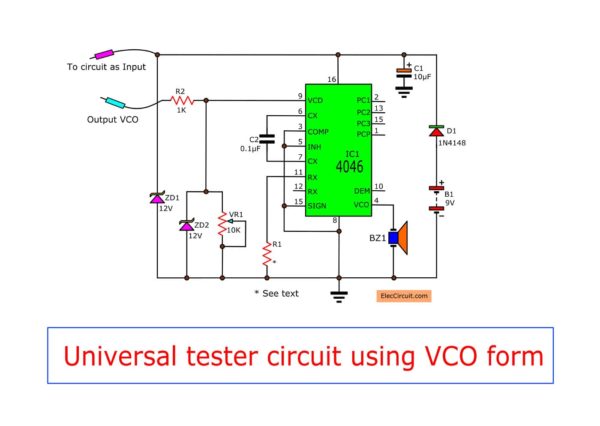

This is a Universal tester circuit with VCO or A voltage controlled oscillator circuit called VCO. The voltage signal level from input to control a number of frequencies that generate an output, or the output frequency transform by voltage.

The basis of a function generators circuit, or an oscillator generator circuit applied in testing a lot of circuits. It can generate frequency to provides the Square wave, triangle wave, or sine wave.

The circuit in Figure 1. It is the VCO circuit to test the working of the electronics circuit. Which the maximum generated frequency about 1.2 kHz. For testing voltage under 9 volts.

Moreover, the first probe will connect directly to a 9V battery terminal to the circuit tested or is input. Next, another probe is a tester for the voltage level that out of from the tested circuit or its output.

Figure 1 Universal tester circuit with VCO

This working principle

First, the working of the circuit has the IC1-CD4046. It is a CMOS MICROPOWER phase-locked loops IC. It will be a Frequency generator controlled by voltage.

While no voltage at pin 9 of IC1. So the VCO circuit will not produce a different frequency.

Then, with a frequency of up to 1.2 kHz audio output with a piezo-BZ1. We can determine the output frequency by C1, and the resistor-R1.

Which R1 connects to pin 11 of IC1. It controlled the greatest frequency. But if we connect the R1 to pin 12, the output will be the lowest frequency.

\

Next, the Zener diode-ZD1 and ZD2 prevent damage from the incoming voltage at the input of VCO. Then, the potentiometer – VR1 adjusts the current level that we is testing.

This is useful when testing the circuit with high impedance. While the work circuit will consume weak current, only about 3 mA.

Besides, the C1 filter current to IC1. At the same time, diode D1 is connecting to block the wrong power supply terminal.

How to build this circuit

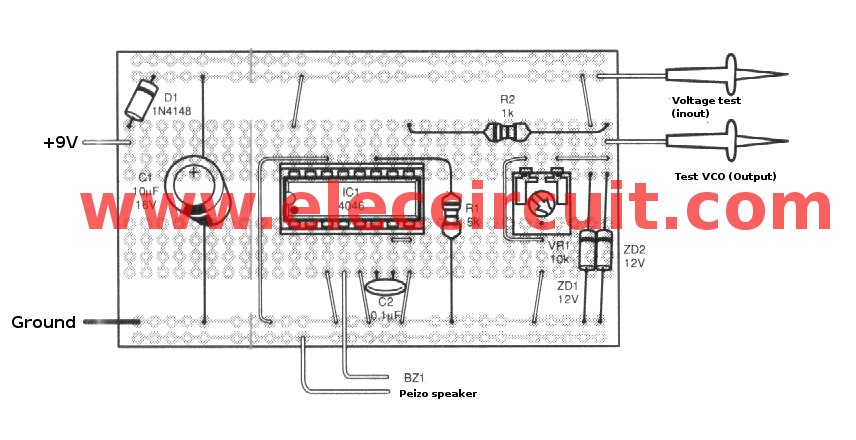

We experiment this project on universal PCB as Figure 2. Which has a few components layout.

Figure 2 the components layout of this project.

The components List

Resistors ¼ W +5%

R1: 5K

R2: 1K

VR1: 10K Potentiometer.

Capacitors

C1: 10uF 16V, Electrolytic

C2: 0.1uF 50V, Polyester

Semiconductor

D1: 1N4148

ZD1, ZD2: 12V 1W

IC1: CD4046

Others

BZ1: Peizo speaker

Two small probe.

PCB universal.

Related Posts

I love electronics. I have been learning about them through creating simple electronic circuits or small projects. And now I am also having my children do the same. Nevertheless, I hope you found the experiences we shared on this site useful and fulfilling.

I am using the 4046 to run the 4017 I want it to count 1-2-3 and repeat 1-2-3 but I get a clock pules between the repeats, this I don’t want. I can’t find the problem. The 4046 works very good. Can you sow or send? a lay out of the 4017 to do this. Thank You.

Jerry

PS.

The pin # and the output # are confusing, maybe that’s my problem.

I’m glad you can use the CD4046 well. Because my English is pretty bad, I don’t understand the meaning clearly. Do you want to use CD4017? Let’s try this: https://www.eleccircuit.com/led-chaser-circuit/

When you get the result. Please let me know. Thanks.

Overall, as a DJ, a SoundCloud downloader is an invaluable tool that helps me deliver a unique and exciting musical experience to my audience.